Microprocessori

Microprocessori

L’idea della fattibilità del microprocessore – ossia dell’intera unità centrale di elaborazione (CPU, Central processing unit) di un computer su un singolo chip – circola già a metà degli anni Sessanta del Novecento, quando alcuni eventi importanti indirizzano la microelettronica sul percorso che porterà alla sua realizzazione: le invenzioni del processo planare e del circuito integrato, e quella del circuito integrato metal-oxide semiconductor (MOS) con gate autoallineante.

Il processo planare, realizzato da John Hoerni nel 1958 alla Fairchild semiconductor, è l’invenzione più rilevante, perché incorpora tutti i principî chiave ancora attualmente in uso e consiste nella fabbricazione simultanea di centinaia di transistori sulla superficie di una fetta di silicio monocristallino. I transistori al silicio, tra l’altro molto più veloci di quelli al germanio fino ad allora utilizzati, sono disposti uno accanto all’altro in una matrice a due dimensioni, con una drastica riduzione del costo di fabbricazione. Dal processo planare al circuito integrato il passo è breve, in quanto è necessario soltanto connettere i transistori tra loro, direttamente sulla fetta di silicio. Il primo circuito integrato fu realizzato nello stesso anno da Jack Kilby della Texas instruments, seguito, pochi mesi dopo, da Robert Noyce della Fairchild, al quale si deve il primo circuito integrato commerciale. Per potere realizzare un microprocessore su un solo chip occorrevano ancora poche altre innovazioni fondamentali.

I primi anni Sessanta sono dominati dai transistori e dai circuiti integrati bipolari ma, a metà del decennio, comincia a diffondersi il nuovo transistore a metallo ossido semiconduttore MOS. I primi dispositivi MOS, lenti e poco affidabili, migliorano notevolmente grazie a una nuova tecnologia sviluppata nel 1968 da Federico Faggin dopo uno studio preliminare svolto da Tom Klein alla Fairchild. Si tratta del processo silicon gate technology, che consente di realizzare circuiti integrati MOS, con gate autoallineante, più veloci, piccoli e affidabili dei precedenti, che presto entreranno in competizione con i circuiti bipolari. Oggi quasi tutti i circuiti integrati sono realizzati con transistori MOS con gate al silicio.

I primi circuiti integrati hanno poche porte logiche, tuttavia già a metà degli anni Sessanta è possibile integrare funzioni più complesse – quali contatori, addizionatori, moltiplicatori – che richiedono decine di porte logiche. Con questi dispositivi sarà possibile, alla fine del decennio, realizzare una piccola CPU in un solo circuito stampato. La strategia dell’industria dei semiconduttori, applicata fin dall’inizio, sarà quella di aumentare il diametro delle fette di silicio e l’area del chip, riducendo le dimensioni dei transistori. In questo modo si possono mettere più chip in una fetta di silicio, ciascuno contenente un numero maggiore di transistori sempre più veloci.

Nascita ed evoluzione del microprocessore

Nell’aprile 1969 la ditta giapponese di calcolatrici da tavolo Busicom valuta l’opportunità di commissionare all’azienda Intel alcuni circuiti integrati, basati su un progetto proprietario, per realizzare un computer specializzato, con macroistruzioni decimali immagazzinate in una memoria di sola lettura (ROM, Read-only memory) e dati immagazzinati in registri a scorrimento (shift registers). L’intero sistema è suddiviso in sette chip diversi, con cui costruire una famiglia di prodotti di complessità variabile, dalle calcolatrici da tavolo con stampante fino alle macchine contabili. Ted Hoff, direttore del reparto di ricerca applicativa della Intel, esplora architetture alternative più semplici, che possano usare la nuova memoria ad accesso casuale (RAM, Random access memory) dinamica a tre transistor per cella, al posto dei registri a scorrimento che richiedono sei transistori per cella. Con la collaborazione di Stanley Mazor e la consulenza della Busicom, Hoff concepisce l’architettura di un computer di uso generale più semplice a 4 bit, consistente in una CPU, in seguito denominata 4004, e in tre chip di memoria e di ingresso-uscita chiamati 4001, 4002 e 4003 (detti famiglia MCS-4).

Nell’aprile 1970 Faggin viene assunto dalla Intel come capo del progetto Busicom, in sostituzione di Hoff e Mazor impegnati in altre attività. Egli completa l’architettura e sviluppa una nuova metodologia di progetto, essenziale per l’implementazione dei circuiti a logica casuale con la tecnologia silicon gate, progettando i quattro chip con l’assistenza dell’ingegnere della Busicom Masatoshi Shima. Nel marzo 1971 i chip sono funzionanti e il mese seguente inizia la produzione del primo prodotto, una calcolatrice da tavolo con stampante.

Il 4004 è un microprocessore con architettura a 4 bit – ossia in grado di elaborarne 4 contemporaneamente – costituito da 2300 transistori realizzati con un processo litografico che consente dimensioni minime di 8 μm (ca. un decimo dello spessore di un capello). È in grado, inoltre, di eseguire 100.000 istruzioni al secondo e viene applicato inizialmente in sistemi di controllo per pompe di benzina, semafori, analizzatori automatici del sangue e macchine da calcolo. In poco più di trent’anni, l’industria dei semiconduttori ha prodotto centinaia di tipi diversi di microprocessori, aumentandone progressivamente la velocità, il numero di bit trattati in parallelo e la complessità.

Di seguito si fornirà un cenno sui microprocessori più importanti dal punto di vista sia dell’innovazione tecnologica, sia del successo di mercato.

Nove mesi dopo il chip della Intel, la Rockwell introduce il microprocessore PPS-4, realizzato con una tecnologia differente ma con prestazioni equivalenti. Rimane invece a livello di annuncio la CPU su singolo chip della Texas instruments, rivelatasi successivamente non funzionante, che tuttavia frutterà a Gary W. Boone e Michael J. Cochran della Texas un contestato brevetto.

Nel gennaio 1971 Faggin e Hal Feeney iniziano il progetto dell’8008, il primo microprocessore a 8 bit con circa 3500 transistori, che integra in un solo chip la CPU progettata dalla Datapoint per un terminale intelligente. L’8008 è introdotto sul mercato nell’aprile 1972 e applicato in terminali intelligenti e calcolatrici programmabili, diventando l’archetipo dei microprocessori, così come la famiglia MCS-4 lo è dei microcontrollori.

Un anno dopo Faggin progetta, insieme a Masatoshi Shima, un microprocessore a 8 bit di seconda generazione, l’8080, che sarà introdotto sul mercato nel 1974 ottenendo grande successo. Il numero di transistori sale a seimila, e il passo litografico scende a 6 μm, mentre il funzionamento a 2 MHz consente di eseguire seicentoquarantamila istruzioni al secondo. L’8080 rende finalmente possibili molte applicazioni in precedenza precluse dalla scarsa velocità dei microprocessori di prima generazione, in particolare i computer per impiego non professionale, antesignani dei personal computer. Questi troveranno la loro piena espressione nei microprocessori di seconda generazione, quali lo Z80 e il 6502 della MOS Technologies usato nell’Apple II, tutti operanti su 8 bit.

Con l’introduzione di nuovi, più potenti tipi di microprocessori, le applicazioni si moltiplicano. Sei mesi dopo l’8080, entra nel mercato dei microprocessori la Motorola con il 6800, progettato da Tom Bennett, che necessita di una sola tensione di alimentazione e sarà utilizzato nelle automobili General motors e Ford. Nel 1976 la Zilog introduce lo Z80 e, l’anno successivo, la Intel annuncia l’8048, il primo microcontrollore in un solo chip, seguita dalla Zilog con il microcontrollore Z8.

Microprocessori a 16 bit

Alle architetture a 4 e 8 bit segue quella a 16 bit, in grado di operare su 16 bit in parallelo, mentre il passo litografico si riduce a 4 μm. Il primo microprocessore di successo di questa categoria è l’Intel 8086, introdotto nel 1978, seguito sei mesi dopo dallo Zilog Z8000 a 4 MHz, il primo microprocessore con memoria virtuale.

Nel 1979 la Intel introduce l’8088, una versione più semplice ed economica dell’8086, con il quale è realizzato il primo personal computer dell’IBM. Segue la Motorola con il 68000, il primo microprocessore realizzato con microistruzioni e architettura a 16/32 bit, funzionante da 4 a 12,5 MHz, che raggiunge prestazioni elevate grazie a istruzioni in formato variabile e a più modi di indirizzamento. Questa strategia continuerà per tutti gli anni Ottanta, portando a repertori di istruzioni sempre più complessi.

Malgrado l’oggettiva superiorità del 68000 rispetto all’8088, nel 1979 la IBM prende la storica decisione di produrre un personal computer (che sarà introdotto nel 1981 sul mercato) basato sull’8088, promuovendone l’adozione per il lavoro d’ufficio e facendo diventare l’architettura di questo chip lo standard dell’industria. Il personal computer diviene in tal modo l’applicazione centrale del microprocessore, favorendone lo spettacolare progresso.

La vasta popolarità raggiunta dall’8088 e dai suoi successori – tra i quali l’80286 del 1982, con centotrentaquattromila transistori in litografia a 2,5 μm, funzionante a 8÷12 MHz e in grado di indirizzare 16 MB di memoria – determinerà la nascita di una fiorente industria di cloni: microprocessori in grado di eseguire lo stesso software scritto per la famiglia ×86 Intel ma con caratteristiche spesso superiori. I primi, nel 1985, sono i chip V20 e V30 della NEC (Nippon electric company), compatibili rispettivamente con l’8088 e con l’8086 e più veloci del 20%. Seguiranno le società AMD (Advanced micro devices), Cyrix, IBM.

Pipeline e memoria cache

Al preciso scopo di aumentare la velocità di funzionamento dei microprocessori vengono sviluppate nuove tecniche hardware e software.

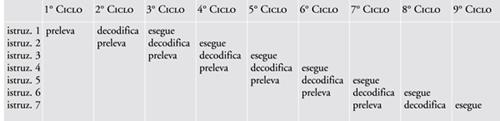

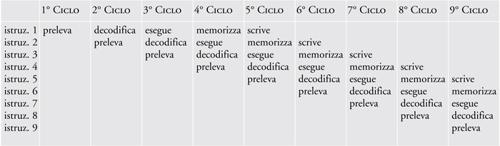

Dal punto di vista hardware, i continui progressi nella litografia consentono di aumentare costantemente il numero di transistori integrati in un singolo chip, secondo la cosiddetta legge di Moore che, già nel 1965, prevedeva un raddoppio della densità dei componenti ogni dodici mesi. Si passa così dalle migliaia di transistori per chip, consentiti dall’integrazione su larga scala (LSI, Large scale integration) dei primi anni Settanta del XX sec., alle centinaia di migliaia della integrazione su larghissima scala (VLSI, Very large scale integration) della metà degli anni Ottanta. La capacità di integrare centinaia di migliaia di transistori permette di utilizzare soluzioni architetturali di avanguardia, a partire da pipeline (tubazione) e memoria cache. Mentre le prime CPU elaboravano le successive istruzioni di programma in modo sequenziale attraverso le fasi di prelievo, decodifica ed esecuzione (tab. 1), quelle dotate di pipeline eseguono simultaneamente più istruzioni, ciascuna a uno stadio diverso nella sua sequenza di elaborazione (tab. 2), con un notevole aumento del numero di istruzioni elaborate per secondo.

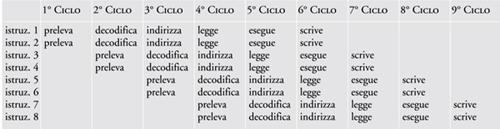

In particolare la tecnica consente, a parte i primi e gli ultimi cicli, di eseguire in un ciclo tante istruzioni quante sono le fasi in cui è stata frazionata l’esecuzione di un’istruzione. La tendenza costante sarà quindi quella di aumentare tale numero di fasi – detto anche profondità della pipeline – realizzando le cosiddette pipeline estese (nella tab. 3 è riportato lo schema di una pipeline a cinque stadi).

Per risolvere situazioni critiche quali le istruzioni di salto, saranno poi sviluppate varie strategie tra cui i salti ritardati, la previsione dei salti e l’esecuzione di altre istruzioni durante i tempi dei salti ritardati.

La memoria cache è una memoria piccola e veloce inserita nel microprocessore (a bordo), che conserva istruzioni e dati usati più spesso oppure di recente, rendendo più veloce l’accesso alle informazioni richieste. Quando le istruzioni o i dati richiesti dal microprocessore sono presenti nella cache, il tempo necessario per richiamarli è di gran lunga inferiore a quello che sarebbe necessario se essi stessi fossero presenti nella memoria principale. La cache, se usata in modo opportuno, determina un netto miglioramento delle prestazioni, riducendo il tempo di esecuzione di un’istruzione. Naturalmente, al crescere della quantità di cache installata nel sistema, aumentano le probabilità che il processore trovi le informazioni necessarie: in un microprocessore contemporaneo in più del 95% dei casi le istruzioni e i dati richiesti da un programma si trovano nella cache.

Le prime memorie cache contengono istruzioni per un massimo di 256 byte e, successivamente, anche dati (cache unificate); più tardi saranno ingrandite e costituite da due porzioni separate, una per le istruzioni e l’altra per i dati (cache divise). A metà degli anni Novanta del XX sec. un tipico microprocessore avrà 8÷16 kB di cache, sia di istruzioni sia di dati. Contemporaneamente si passa dalla cache diretta, che conserva in un unico blocco i dati delle aree di memoria più usate, a quella associativa, in grado di conservare più blocchi di dati prelevati da altrettante aree di memoria usate più di frequente. Successivamente sarà inserita nella scheda madre una seconda cache più grande e più lenta, detta cache di secondo livello.

Pipeline e cache vengono applicate per la prima volta nel Motorola 68020 del 1984, uno dei primi microprocessori completamente a 32 bit, in grado quindi di utilizzare una memoria di 4 GB. Dotato di duecentomila transistori in litografia a 2 μm, questo microprocessore funziona a 16 MHz, possiede una pipeline a tre stadi, una memoria cache di istruzioni di 256 byte e usa la memoria virtuale. È seguito un anno dopo dal primo microprocessore a 32 bit della Intel, l’80386, anch’esso con pipeline a tre stadi, in grado di svolgere 10 milioni di operazioni al secondo (MIPS, Million instructions per second), che sarà premiato da un lungo successo di mercato e clonato da diverse imprese concorrenti (AMD, IBM e Cyrix). Contemporaneamente si sviluppano circuiti che permettono frequenze di funzionamento sempre più elevate, fino a raggiungere 1 GHz nel 1999.

Architetture RISC

Nel tentativo di migliorare progressivamente le prestazioni dei microprocessori, mantenendo allo stesso tempo la compatibilità con il software delle precedenti versioni, le architetture dei computer diventano sempre più complesse. In particolare, aumentano il numero e la complessità delle istruzioni elementari cablate direttamente in hardware (microcodice), creando generazioni di computer a repertorio complesso di istruzioni (CISC, complex instruction set computer). Tuttavia, i microprocessori CISC rendono sempre più difficile il progetto di compilatori efficienti per linguaggi d’alto livello, vanificando il vantaggio di avere istruzioni molto specializzate.

Emerge così un differente modello di interazione tra hardware, firmware e software, noto come computer a repertorio ridotto di istruzioni (RISC, Reduced instruction set computer), che usa un numero inferiore di istruzioni, ciascuna di lunghezza standard e in grado di svolgere una funzione relativamente elementare, permettendo l’utilizzazione di compilatori ottimizzati. Vengono ridotte le routine in microcodice e il controllo di basso livello della macchina è restituito al software. Ne consegue un microprocessore di progettazione più semplice, che può funzionare più velocemente.

Questo approccio viene applicato in modo estensivo a partire dalla metà degli anni Ottanta con architetture RISC aventi sia pipeline sia memoria cache e compilatori in grado di gestire efficacemente la pipeline.

I primi microprocessori RISC sono prodotti a partire dal 1980 dalle Università di California a Berkeley (RISC I/II) e a Stanford (MIPS 2000).

Architetture superscalari

Nella continua ricerca di architetture sempre più veloci, l’industria dei microprocessori, a partire dagli anni Novanta, adotta un’altra tecnica di avanguardia: la progettazione superscalare, che dà luogo alle cosiddette architetture post-RISC. Mentre in una pipeline tradizionale le diverse istruzioni sono eseguite da una sola unità di elaborazione, indipendentemente dal numero di stadi in cui sono suddivise, in un processore superscalare lavorano in parallelo più unità di elaborazione, ciascuna alimentata da una propria pipeline. Da questo punto di vista, la Intel classifica i suoi processori secondo diversi livelli: per esempio, un processore Pentium2 può eseguire due istruzioni a ogni ciclo di clock (tab. 4), uno di livello 3 (quale il Pentium Pro) ne esegue tre.

Per ottimizzare il livello di parallelismo è necessario gestire le dipendenze tra le varie istruzioni in modo da mantenere riempita la pipeline. A tale scopo vengono sviluppate diverse strategie: esecuzione fuori ordine, ridenominazione dei registri, svolgimento di cicli, previsione dinamica di salto con tabella della storia dei salti, esecuzione speculativa e schedulazione dinamica delle istruzioni.

Tra i primi microprocessori superscalari commerciali, introdotti agli inizi degli anni Novanta, c’è il SuperSPARC I della Sun microsystems. Si tratta di un microprocessore RISC a 32 bit altamente integrato a elevate prestazioni, progettato in base al più avanzato processo BiCMOS disponibile. Viene usato in applicazioni che vanno da macchine desktop uniprocessore a grandi server multiprocessore. Raggiunge prestazioni di 1,13 SPECint95 e 1,38 SPECfp95 a 40 MHz, che saliranno a 3,11 SPECint95, 3,10 SPECfp95 e 75 MHz nel successivo SuperSPARC II, con cache di secondo livello da 1 MB. Altre architetture RISC di successo saranno varate da AMD, Hewlett packard, Digital equipment e dalle stesse Intel e Motorola, e poco alla volta i principî RISC saranno adottati da tutta l’industria. Nel 1989 la litografia raggiunge il traguardo del micrometro con il microprocessore a 32 bit Intel 80486, che contiene 1,2 milioni di transistori, funziona a 25 MHz ed esegue 20 MIPS. È il primo che integra un coprocessore matematico per i calcoli in virgola mobile, in precedenza costituito da un chip separato.

Gli anni Novanta

Negli anni Novanta, con l’intensificarsi della competizione tra Intel e alcune imprese concorrenti, si accelera anche il ritmo dell’innovazione. Nel 1992, in risposta alle esigenze della grafica a elevate prestazioni, la MIPS Technologies introduce l’R4000, uno dei più veloci processori RISC su chip singolo con architettura super-pipeline. Il clock esterno a 50 MHz viene duplicato nella CPU per pilotare le pipeline profonde a 100 MHz. I bus dati e indirizzi sono a 64 bit e multiplati; sono presenti due cache separate da 8 kB per istruzioni a mappatura diretta e per dati e un controllore di cache di secondo livello su chip. Ne saranno realizzate diverse varianti, che renderanno popolare l’architettura MIPS nel mercato dei microprocessori incorporati in diversi dispositivi.

Il traguardo di 100 MIPS viene raggiunto nel 1993 dalla Intel con l’introduzione del Pentium, il successore dell’80486, che ha 3,1 milioni di transistori in litografia a 0,8 μm e frequenza di 60 MHz, e usa la tecnologia BiCMOS che consente velocità più elevate della CMOS.

Dal 1993 al 1995 si registra il progresso più rapido nella storia dei semiconduttori, che vede le dimensioni dei transistori ridursi da 0,8 a 0,35 μm. Questo consente di integrare 5,5 milioni di transistori nel Pentium Pro, con il quale inizia nel 1996 la sesta generazione di microprocessori Intel. Per la prima volta la cache di secondo livello (di 256 kB÷2 MB) si trova nel contenitore del microprocessore anziché sulla scheda madre, il che ne aumenta la velocità di funzionamento. Il Pentium Pro, che utilizza una memoria principale di 64 GB grazie all’aggiunta di quattro linee indirizzi e funziona alla frequenza di 200 MHz, sarà adottato in prevalenza da server e sistemi multiprocessore.

Nel 1995 la Sun introduce, nell’UltraSPARC-I a 64 bit, il repertorio di istruzioni visuali (VIS, Visual instruction set), che permette l’elaborazione diretta degli elementi costitutivi delle immagini (pixel). Esso fornisce avanzate prestazioni multimediali, tra cui una compressione/decompressione video in tempo reale che consente velocità di movimenti conformi agli standard del Motion picture experts group (MPEG), senza supporto di hardware aggiuntivo. L’UltraSPARC-I è un processore RISC superscalare che può inviare quattro istruzioni contemporaneamente alle nove unità di elaborazione in-terne. È realizzato in tecnologia a 0,50 μm, ha prestazioni di 7,72 SPECint95 e 11,4 SPECfp95 e opera a 167÷200 MHz, con cache di secondo livello da 1 MB.

Nello stesso periodo si sviluppano anche nuovi criteri per misurare la velocità di calcolo di un microprocessore, che portano a sostituire la vecchia unità MIPS con le più adeguate SPECint95 e SPECfp95, che misurano le prestazioni in elaborazioni intensive su numeri rispettivamente interi e in virgola mobile e che si basano su test software relativi non solo al processore, ma anche all’architettura della memoria e del compilatore. Queste unità cederanno a loro volta il posto, alla fine del decennio, alle nuove SPECint2000 e SPECfp2000, basate su test diversi, che stanno alle vecchie nei rapporti di circa 12:1 e 10:1.

Il primo microprocessore che, alla fine del 1996, raggiunge la frequenza di 500 MHz è l’avanzatissimo Alpha 21164 della Digital equipment, con 9,3 milioni di transistori. Esso possiede una memoria cache di secondo livello di 96 kB, in aggiunta a una cache di istruzioni e una di dati di 8 kB ciascuna. Ha una pipeline a 7 stadi e un’architettura a 64 bit, che si rivelerà particolarmente utile nelle stazioni di lavoro e nei server, che richiedono una grafica di elevata qualità.

Anche l’architettura SPARC determina un fiorente mercato di prodotti compatibili: alla fine del 1996 la Fujitsu Microelectronics introduce il microprocessore TurboSPARC, di frequenza (170 MHz) e prestazioni (3,53 SPECint95 e 3,00 SPECfp95) nettamente superiori a quelle dei microprocessori SPARC contemporanei. Ha una pipeline a nove stadi, una memoria cache per istruzioni e una per dati entrambe da 16 kB e una cache di secondo livello da 1 MB. Particolarmente contenuto il consumo energetico, di soli 7 watt.

Nel 1997 la Intel introduce, con il Pentium II in litografia a 0,35 μm, il primo microprocessore che esegue direttamente istruzioni multimediali (MMX, Multi-media extensions), in grado quindi di migliorare l’esecuzione dei programmi che si avvalgono consistentemente di audio, grafica e animazioni. Esso può indirizzare una memoria fino a 4 GB (grazie a una cache di secondo livello di 512 kB), funziona a frequenze di 233÷450 MHz e si diversificherà l’anno successivo nel più economico e lento Celeron, per stazioni di lavoro commerciali, e nel più potente Xeon per il mercato dei server.

Alla fine del 1998 i Bell labs annunciano un tipo potenziato di transistore ad arseniuro di gallio (GaAs) a basso consumo e alta velocità, che migliora le prestazioni delle porte logiche basate su di esso, senza tuttavia riuscire a mantenere le molte promesse di questa tecnologia. Nello stesso periodo la Intel cede la licenza del suo classico Pentium ai laboratori Sandia, che ne svilupperanno versioni adatte per l’impiego nello spazio in collaborazione con altre agenzie governative e militari statunitensi, ottenendo in cambio i diritti per la progettazione di chip a prova di radiazione, che in seguito vende per applicazioni commerciali.

Microprocessori in Russia

Importanti realizzazioni si hanno in questi anni anche fuori degli Stati Uniti. Nel 1998 il centro di ricerche russo Module progetta il processore NM6403 ad architettura superscalare, che impiega la tecnologia CMOS a 0,50 μm della Samsung e quella ASIC a 0,24 μm della Fujitsu. Esso realizza la prima implementazione hardware dell’architettura NeuroMatrix, in grado di emulare le reti neurali artificiali ed elaborare le immagini video, e integra un nucleo RISC a 32/64 bit e un coprocessore vettoriale in grado di elaborare segnali digitali lunghi da 1 a 64 bit, consentendo calcoli su matrici con elementi di lunghezza (in bit) variabile. Il supporto esteso di operazioni su matrici consente di usarlo nella elaborazione di segnali digitali.

L’anno successivo la società russa Elbrus international annuncia il nuovo, rivoluzionario microprocessore E2K, versione commerciale del modello già impiegato in sistemi spaziali e difensivi. Dichiara prestazioni superiori a quelle degli altri processori esistenti e pianificati – pur necessitando di una minore potenza e occupando una minore superficie di silicio; esso accetta inoltre tutto il software scritto per MS DOS e Windows. Tuttavia difficoltà finanziarie impediranno la produzione dell’E2K su scala commerciale.

Microprocessori più recenti

Nel 1998 la Fujitsu realizza lo SPARC64 GP, un processore RISC a 64 bit superscalare con super-pipeline caratterizzato da un’avanzata tecnica di predizione dei salti. Esso contiene 17,6 milioni di transistori in litografia a 0,24 μm, ha frequenze di 225÷296 MHz e prestazioni di 19,2 SPECint95 e 30,5 SPECfp95 a 296 MHz con cache di secondo livello da 8 MB.

All’inizio del 1999 Silicon Graphics introduce il nuovo processore MIPS R12000 a 300 MHz per le stazioni di lavoro grafiche Octane. Le prestazioni, con cache di secondo livello da 2 MB, sono SPECfp95 27,5 e SPECint95 17,3, leggermente inferiori a quelle dello stesso processore prodotto alla fine del 1998 dalla giapponese NEC.

Lo stesso anno il K7 della AMD è il primo microprocessore a varcare la barriera di 1 GHz, seguito nel 2002 dall’Athlon XP 3000+, il processore per computer desktop dalle prestazioni più elevate, in particolare nel settore della multimedialità. Sempre nel 1999, la Intel introduce il Pentium III, che nella versione Coppermine fornisce 442 SPECint2000 e 333 SPECfp2000 a 1 GHz; oltre alle istruzioni MMX, implementa le nuove estensioni Internet Streaming SIMD, che accelerano la pipeline della grafica tridimensionale di un fattore due, mentre consentono la codifica MPEG-2 in tempo reale.

All’inizio del 2000 la piccola società californiana Transmeta applica nel suo innovativo processore Crusoe l’architettura detta parola istruzione molto lunga (VLIW, Very long instruction word), sviluppata dalla IBM a metà degli anni Ottanta. A differenza di un processore super-scalare, uno VLIW non deve esaminare se le istruzioni possano essere eseguite in parallelo, dato che questa informazione è già codificata nella parola istruzione, costituita da una lunga sequenza di comandi. La tecnica riduce i costi e consente velocità di elaborazione più elevate, a parità di potenza dissipata, permettendo di eseguire fino a quattro operazioni in ogni ciclo. Crusoe si rivela particolarmente adatto per la navigazione in Internet da postazioni mobili ed esegue il repertorio di istruzioni dei processori Intel ×86 traducendolo nella propria architettura VLIW.

Dal 2001 è disponibile la CPU Alpha 21264B di Compaq/Digital, con 15,2 milioni di transistori in tecnologia da 0,18 μm, che eroga una potenza di 544 SPECint2000 e 658 SPECfp2000 a 833 MHz. Leggermente inferiori (535 SPECint2000 e 558 SPECfp2000, a 1,5 GHz) sono le prestazioni del quasi contemporaneo Pentium IV, con 42 milioni di transistori fabbricati con il processo CMOS a 0,18 μm, superficie di 217 mm2, e consumo di 50 watt. È il primo processore ×86 di progetto completamente nuovo dopo il Pentium Pro. La microarchitettura NetBurst raddoppia la profondità di pipeline del Pentium III a 20 stadi; in aggiunta alla cache dati di primo livello di 8 kB esso include una cache di traccia dell’esecuzione, che memorizza fino a 12.000 micro-operazioni decodificate nell’ordine dell’esecuzione del programma. La cache di secondo livello da 256 kB impiega un’interfaccia da 256 bit che sviluppa una velocità di trasferimento dati di 48 GB/sec a 1,5 GHz. Il chip dispone di registri in virgola mobile a 128 bit e di un registro per i movimenti dei dati. L’architettura NetBurst introduce le estensioni Internet Streaming SIMD 2, che ampliano le precedenti SIMD con l’aggiunta di 144 nuove istruzioni per l’aritmetica intera a 128 bit e le operazioni in virgola mobile e doppia precisione. Il bus di sistema fornisce una larghezza di banda di 3,2 GB/sec, valore triplo di quello del Pentium III. Due unità aritmetico-logiche sono pilotate da un clock a una frequenza doppia di quella del processore. Oggi sono disponibili Pentium IV fabbricati con litografia a 0,13 μm che funzionano a 2,8 GHz e sono stati già presentati campioni sperimentali funzionanti a 4 GHz.

La Sun potenzia costantemente l’architettura SPARC: l’UltraSPARC-IIi del 1997 incorpora su chip singolo un’unità centrale di elaborazione, un’interfaccia per bus PCI e un controllore di memoria. È sviluppato in tecnologia a 0,35 μm e contiene una cache di secondo livello da 0,25÷2 MB. Le frequenze operative sono 270÷440 MHz e le prestazioni 18,1 SPECint95 e 22,7 SPECfp95, a 440 MHz con cache da 2 MB. Segue l’UltraSPARC-II, un processore superscalare ad alte prestazioni e alta integrazione (5,4 milioni di transistori in tecnologia a 0,25 μm), in grado di eseguire fino a quattro istruzioni per ciclo anche in presenza di salti condizionati e assenza dei dati necessari nella cache, permettendo l’elaborazione di immagini bidimensionali e tridimensionali, compressione e decompressione video ed effetti video ottenuti con il repertorio di istruzioni VIS. Le frequenze operative sono 250÷480 MHz e le prestazioni 234 SPECint2000, 291 SPECfp2000 a 400 MHz, con cache di secondo livello da 8 MB.

A partire dalla fine del 2000 è disponibile il modello UltraSPARC-III, con circa 29 milioni di transistori in tecnologia a 0,18 μm, in grado di collegarsi a centinaia di processori in un singolo sistema, grazie a un controllore incorporato che facilita le contese tra i processori per l’accesso alla memoria. Uno switch controlla il percorso dei dati sul bus di sistema tra la CPU e la memoria e può concentrare i singoli flussi di dati in un flusso unico a velocità relativamente alte. Le frequenze sono 600÷900 MHz e le prestazioni (con cache da 8 MB) vanno da 395 SPECint2000 e 421 SPECfp2000 a 750 MHz fino a 467 SPECint2000 e 482 SPECfp2000 a 900 MHz. La versione Cu contiene interconnessioni in rame che migliorano la trasmissione dei segnali e il consumo (ca. 70 watt) e porte logiche a 0,09 μm (90 nm), che rendono più veloci le prestazioni.

Per competere con i più potenti processori Alpha e UltraSPARC usati in server e stazioni di lavoro, nel 2000 la Intel introduce Itanium (detto in precedenza Merced), il primo membro della nuova famiglia di microprocessori a 64 bit, con 25 milioni di transistori in litografia a 0,18 μm, che implementa la tecnologia EPIC Elaborazione a istruzioni esplicitamente parallele (Explicitely parallel instruction computing), derivata dalla VLIW e in grado di trattare fino a 20 istruzioni in ogni ciclo di clock, con le quali alimenta unità funzionali multiple presenti nel chip. Itanium opera a 600÷800 MHz, è il primo microprocessore dotato di tre livelli di memoria cache nello stesso chip e raggiunge una potenza di 45 SPECint95 e 70 SPECfp95 (o 6 GFlops). Esso può indirizzare una memoria principale di 16 GB, usa una pipeline con istruzioni a 10 stadi, ha una superficie di 300 mm2 e consuma 60 watt.

A metà del 2002 la Intel commercializza l’Itanium 2 a 1 GHz, con 221 milioni di transistori (25 milioni dei quali per la logica e il resto per la memoria) in una superficie di 421 mm2 e tecnologia a 0,18 μm. Possiede 328 registri e 11 issue port, che gli consentono di accettare altrettante istruzioni in parallelo, ciascuna con una pipeline a 8 stadi. Dispone anch’esso di tre livelli di cache per un totale di 3,3 MB, con una banda sostenibile di 64 GB/sec. Il bus di sistema ha 128 linee a 400 MHz, con una banda quindi di 6,4 GB/sec. I salti casuali sono minimizzati con l’ausilio di tre unità di previsione di salto ed è mantenuto un alto parallelismo grazie a sei unità aritmetiche di uso generale, una multimediale a SIMD, due di caricamento, due di memorizzazione, due in virgola mobile e una di esecuzione che permette di mantenere la compatibilità software con il codice ×86. L’architettura utilizza tecniche di rilevamento e correzione di errori, con capacità di recupero. Funziona con una tensione di alimentazione di 1,5 volt, può eseguire fino a 6 miliardi di istruzioni al secondo (GIPS), dissipando 130 watt. È usato per costruire potenti computer aziendali e supercomputer contenenti fino a qualche migliaio di microprocessori: per esempio, il supercomputer della National Science Foundation, attualmente in via di sviluppo, avrà 3300 microprocessori Itanium e Itanium 2, una prestazione di 13,6 mila miliardi di operazioni al secondo (TOPS) e potrà indirizzare 450.000 miliardi (Terabyte) di dati.

Microprocessori per usi particolari

I microprocessori di uso generale presenti nei personal computer, nei server e in altri prodotti programmabili dall’utente, dei quali ci siamo interessati finora, costituiscono soltanto una delle sei categorie di dispositivi basati sul microprocessore. Le altre categorie sono: i microcontrollori, i circuiti integrati per applicazioni specifiche (ASIC, Application specific integrated circuits), i prodotti standard per applicazioni specifiche (ASSP, Application specific standard products), gli elaboratori di segnali digitali (DSP, Digital signal processors) e i microprocessori specializzati.

I microprocessori di uso generale sono all’avanguardia tecnologica, hanno velocità più alte e prezzi più elevati delle altre categorie, riflettendo sia il valore della compatibilità software sia le particolari condizioni competitive del mercato. Essi rappresentano, tuttavia, meno del 5% dei microprocessori venduti nel mondo. Microprocessori più semplici a prezzi molto più bassi sono al centro di migliaia di tipi diversi di microcontrollori, ASSP e ASIC. La gamma dei chip che contiene uno o più microprocessori è vastissima e va dall’Itanium 2, che costa più di 4000 euro, ai microcontrollori a 4 bit usati nel telecomando televisivo, che costano meno di 30 centesimi l’uno.

Un microcontrollore è un computer in un solo chip, che contiene un microprocessore, una certa quantità di memoria ROM e RAM e logica di controllo per una varietà di periferiche, alcune delle quali possono essere altamente specializzate. I microcontrollori sono assai diffusi: un’automobile ne ha 20÷40 e un tipico personal computer 10÷20, localizzati nella tastiera, nel mouse o nel touchpad, nel disco magnetico e anche nella batteria al litio per gestirne la carica e scarica in modo da garantirne la sicurezza e la durata. Più di 5 miliardi di microcontrollori sono venduti ogni anno per uso personale, che rappresenta l’area applicativa più vasta. Calcolatrici, orologi, videogiochi, pager, smartcard, telefonini, elettrodomestici e così via, hanno tutti almeno un microcontrollore.

Un ASIC è un chip specializzato a eseguire una funzione specifica per un particolare cliente: per esempio, controllare un telefonino oppure un disco magnetico, una stampante o un videogioco.

Un ASSP è simile a un ASIC ma è un prodotto standard, progettato e disponibile per il mercato generale, anche se, come un ASIC, è specializzato nel compiere una funzione particolare. Può essere, per esempio, un controllore di tastiera, di dischi magnetici, di grafica, e cosi via. Talvolta un ASSP è un microcontrollore standard con l’aggiunta di firmware specializzato. Generalmente ASIC e ASSP contengono uno o più microcontrollori.

Un DSP è un processore specializzato nell’elaborazione di segnali seriali e usato per gli algoritmi specializzati di quasi tutti i prodotti di telecomunicazione: telefoni cellulari, router, controllori seriali, reti locali, elaboratori di voce, immagini e video, eccetera. Negli anni Novanta l’uso di DSP è aumentato rapidamente e attualmente essi rappresentano una categoria importante.

La categoria dei microprocessori specializzati include molti tipi di processori: (a) di ingresso/uscita, grafici, multimediali, di rete, riconfigurabili e così via, tutti progettati per gestire funzioni specializzate meglio di quanto sia possibile con microprocessori di uso generale.

Futuro dei microprocessori

Le caratteristiche dei microprocessori futuri saranno determinate in gran parte dall’interazione di tre elementi fondamentali: tecnologia, applicazioni e architettura.

La sfida tecnologica fondamentale riguarda la legge di Moore. Il raddoppio del numero di transistori per chip ogni anno, che si verificava a metà degli anni Sessanta, avviene oggi ogni 1,5÷2 anni e continuerà a rallentare via via che ci si avvicinerà ai limiti fisici delle dimensioni del transistore MOS. Alla fine del 2002 sono stati prodotti microprocessori sperimentali con litografia a 90 nm, ma la dimensione finale di un transistore MOS non potrà scendere molto al di sotto di 10 nm a causa della natura quantica della materia, che pone difficoltà insormontabili. La strategia di ridurre le dimensioni dei transistori ha quindi i giorni contati, probabilmente ancora 15 anni di vita.

L’altra possibilità per accrescere il numero dei transistori di un chip è di aumentarne le dimensioni: dai 12 mm2 del 4004 si è passati ai 421 mm2 dell’Itanium 2 e si prevede che, nel giro di un quindicennio, i chip più avanzati avranno un’area di 16 cm2. Tuttavia anche in questo caso c’è un limite pratico, poiché le dimensioni del chip non possono superare quelle del prodotto che lo deve usare.

Si lavora inoltre per ridurre le dimensioni esterne dei microprocessori, creando nuovi tipi di incapsulamento che ne limitino le dimensioni totali, rendendoli appena più grandi dello stesso chip. La Intel sta sviluppando la nuova tecnologia BBUL (Bumpless build up layer), un metodo di incapsulamento che costruisce il package attorno al chip e permette di incapsulare più di un chip sullo stesso package.

È l’inizio dei componenti a più strati attivi: sfruttare la terza dimensione è inevitabile, anche se oggi è impossibile prevedere quale sarà la tecnologia vincente nel prossimo futuro. Usando più strati attivi sarà possibile rispettare la legge di Moore per altri 20-30 anni, anche dopo avere raggiunto le dimensioni limite del transistor. Il tempo richiesto per raddoppiare la complessità continuerà però ad aumentare.

Tra circa quarant’anni si prevede che i chip più avanzati avranno tra diecimila e centomila miliardi di transistori, a una frequenza di funzionamento che si avvicinerà a mille miliardi di hertz (1 teraHz). Poiché la luce percorre soltanto 0,3 mm in un milionesimo di milionesimo di secondo (1 ps), un’altra ragione fondamentale per creare strutture tridimensionali è di continuare ad aumentare la velocità di sistema. È ovvio che scambiare segnali tra chip che si trovano a molti centimetri di distanza l’uno dall’altro pregiudicherebbe le prestazioni del sistema, anche se i chip fossero individualmente velocissimi.

Via via che aumenterà la complessità dei chip, si dovranno risolvere altri due difficili problemi: le interconnessioni e l’eliminazione della potenza dissipata. I transistori nell’Itanium 2, per esempio, sono collegati tramite sei strati di alluminio e il chip dissipa 130 watt. Attualmente l’area del chip dedicata alle interconnessioni cresce in modo non lineare con il numero dei transistori, mentre la potenza dissipata è proporzionale al numero di cambiamenti di stato per secondo del chip, moltiplicata per la potenza dissipata in un cambiamento di stato. Perciò, quando le dimensioni del transistor arriveranno al limite fisico, la potenza dissipata per cambiamento di stato non potrà più essere ridotta e il problema della sua dissipazione diventerà particolarmente cruciale. Le difficoltà imposte dalla finitezza della velocità della luce, dalla potenza dissipata e dalla complessità delle interconnessioni avranno un impatto molto più profondo sull’architettura dei futuri microprocessori di quanto sia avvenuto in passato.

Alcune applicazioni pilota influenzano più di altre le nuove architetture. Una di queste è la simulazione in tempo reale di sistemi complessi, essendo spesso meno costoso effettuare una simulazione che non costruire il sistema di prova. Trovare una soluzione adeguata alle applicazioni pilota, malgrado le limitazioni tecnologiche descritte, richiederà livelli sempre più alti di parallelismo e modularità con vari piani gerarchici, dando particolare risalto allo studio di architetture, sia hardware sia software, adatte a questo scopo.

La Intel ha recentemente annunciato che per il 2010 produrrà microprocessori con 10 miliardi di transistori funzionanti a 30 GHz e con la capacità di 1012 operazioni al secondo (1 TOPS). I microprocessori che permetteranno di costruire un supercomputer da 1015 operazioni al secondo (1 POPS) entro i prossimi dieci anni e 1000 POPS per il 2040 lavoreranno tutti in parallelo. Architetture modulari consentiranno anche di integrare in un chip decine e poi centinaia di microprocessori, continuando la marcia verso maggiori prestazioni a costi sempre più bassi.

Oltre ai microprocessori avanzati che saranno usati nei futuri PC, server e supercomputer, nei quali il livello di integrazione e la velocità saranno spinti al limite delle possibilità tecnologiche usando processi di fabbricazione altamente specializzati, vi sono altre direzioni importanti verso le quali sarà incanalato il potenziale della tecnologia dei semiconduttori. Nei prodotti a basso livello di complessità, la tecnologia sarà usata principalmente per ridurre il costo del prodotto, integrando in un solo chip un intero sistema quale un telefonino multimediale o una videocamera. Ciò richiederà di integrare sullo stesso substrato dispositivi diversi quali transistori digitali, analogici, a radio frequenza, di potenza, sensori di immagini, ecc., accelerando una tendenza già in atto da tempo.

Il microprocessore ha trent’anni ma ha ancora una vita lunga di fronte a sé. Benché sia oggi piuttosto difficile immaginare il possibile utilizzo di diecimila miliardi di transistori in un cubetto di silicio, il passato ha ampiamente dimostrato che si possono sempre concepire nuove applicazioni che mettono alla prova le capacità di calcolo disponibili, per quanto potenti esse possano essere. I microprocessori che sono destinati a evolvere da quelli attuali continueranno a essere al centro delle future generazioni di sistemi digitali per almeno altri quarant’anni. I microprocessori basati sul silicio saranno alla fine superati da nuove idee, attualmente agli stadi iniziali di studio – come le nanotecnologie e i computer quantici – oppure ancora in embrione o a venire.

Bibliografia

Antonakos, Stewart 1998: Antonakos, James L. - Stewart, Charles E., Introduction to the Intel family of microprocessors: a hands-on approach utilizing the 80tm86 microprocessor family, Upper Saddle River (N.J.), Prentice-Hall, 1998.

Byman 2000: Byman, Jeremy, Andrew Grove and the Intel Corporation, 2. ed., Greensboro (N.C.), Reynolds, 2000.

Celebrating the microprocessor, “IEEE Micro”, 16, 1996, pp. 2-3.

Crump 2002: Crump,Thomas, A brief history of science as seen through the development of scientific instruments, London, Robinson, 2002 (1. ed.: London, Constable; New York, Carrol and Graf, 2001).

DuPont Chandler 2001: DuPont Chandler, Alfred - Takashi, Hikino - von Nordenflycht, Andrew, Inventing the electronic century: the epic story of the consumer electronics and computer industries, New York-London, Free Press, 2001.

Faggin 2002: Faggin, Federico, Lectio doctoralis, Roma, Università Tor Vergata, 2002.

Forester 1981: Forester, Tom, Microelectronics revolution, Cambridge (Mass.), MIT Press, 1981.

Gallippi 2002: Gallippi, Angelo, Faggin, il padre del chip intelligente, Roma, AdnKronos Scienza e Sanità, 2002.

Greenia 2001: History of computing: an encyclopedia of the people and machines that made computer history, edited by Mark W. Greenia, Sacramento, Lexikon Services, 2001.

Leach 1994: Leach, Cliff, Alpha. A strategic review, Upper Saddle River (N.J.), Prentice-Hall, 1994.

Malone 1995: Malone, Michael S., The microprocessor: a biography, New York, Springer, 1995.

Shurkin 1996: Shurkin, Joel, Engines of the mind: the evolution of the computer from mainframes to microprocessors, New York, Norton, 1996.

Veidenbaum, Kazuki 1999: Innovative architecture for future generation high-performance processors and systems: postproceedings, edited by Alex Veidenbaum, Joe Kazuki, Los Alamitos, IEEE Computer Society, 1999.

Yu 1998: Yu, Albert, Creating the digital future: the secretsof consistent innovation at Intel, New York, Free Press,1998.

Zygmont 2002: Zygmont, Jeffrey, Microchip: an idea, its genesis, and the revolution it created, Cambridge (Mass.), Perseus, 2002.

Siti internet

http://www.intel.com/technology/itj/ (Intel technology journal).

http://www.intel.com/intel/intelis/museum/index.htm (The Intel museum).

http://www.computerhistory.org/ (Computer history museum).