multivibratore

Dispositivo elettronico con due soli stati di funzionamento, generalmente impiegante due stadi amplificatori a transistori (generalmente in circuito integrato), accoppiati in modo che l’ingresso di uno sia collegato con l’uscita dell’altro. I m. sono largamente usati, per es., come generatori di tensioni a impulsi, a onda quadrata e a denti di sega, nei calcolatori elettronici o in strumenti di misura di tipo digitale. Si hanno tre tipi fondamentali di m.: astabili, monostabili, bistabili.

M. astabile

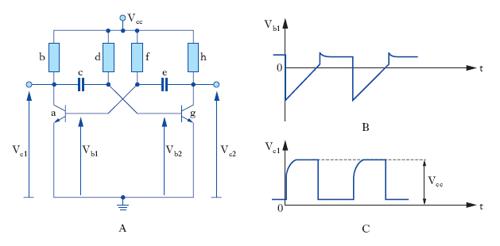

È il tipo dal quale sono derivati tutti gli altri. Il m. astabile (fig. 1A) è in sostanza un amplificatore a resistenza-capacità a due stadi (transistori a, g), con un condensatore d’accoppiamento e fra ingresso e uscita; la reazione che in questo modo si stabilisce ha per risultato di portare alternativamente all’interdizione l’uno o l’altro dei due transistori. L’andamento delle tensioni di base è approssimativamente a dente di sega (fig. 1B), mentre quello delle tensioni di collettore è approssimativamente rettangolare (fig. 1C). Se i resistori di collettore b, h, i resistori di base d, f, e i condensatori d’accoppiamento c, e, sono uguali fra loro, il m. si dice simmetrico, altrimenti si dice asimmetrico; nel primo caso il segnale d’uscita, prelevato da uno dei collettori, è simmetrico (cioè a onda quadra). La frequenza del segnale generato dipende dal valore dei resistori di base e dei condensatori d’accoppiamento. Tale m. è detto astabile perché non ha uno stato di funzionamento stabile, ma i due transistori passano alternativamente dall’interdizione alla saturazione.

M. monostabile

È un m. asimmetrico avente un solo stato di funzionamento stabile e caratterizzato dal fatto che uno dei due transistori è interdetto, mentre l’altro è in saturazione; ciò può essere ottenuto eliminando un condensatore di accoppiamento e la relativa resistenza di base di un m. astabile (c, g in fig. 1A) e collegando con un resistore questa base al collettore dell’altro transistore. Un impulso positivo esterno applicato alla base del transistore interdetto altera questa condizione di equilibrio, alla quale si ritorna dopo un certo tempo, determinato dalla costante di tempo del gruppo resistenza-capacità del circuito; in definitiva, l’impulso di comando dà luogo alla formazione di un solo impulso rettangolare di ampiezza e lunghezza costanti.

M. bistabile

Il m. bistabile (o flip-flop) è un m. avente due possibili stati di funzionamento stabile, caratterizzati dal fatto che uno dei transistori (per es. b in fig. 2) è interdetto, mentre l’altro (a) conduce. Se si applica un impulso negativo alla base di a, la relativa corrente di collettore diminuisce, mentre la tensione aumenta, trasferendo un impulso positivo di tensione alla base di b, che comincia a condurre. La caduta della tensione di collettore nel transistore b, trasferita come impulso negativo alla base di a, determina una reazione positiva con conseguente definitivo passaggio di a all’interdizione e di b alla conduzione. La commutazione del m. si ha così quando viene applicato un impulso di tensione negativo alla base del transistore in conduzione oppure un impulso positivo alla base di transistore interdetto. Tale m. genera in definitiva un impulso per ogni due impulsi applicati alle basi, costituendo una ‘scala di 2’, cioè un divisore di impulsi nel rapporto 2:1; per tale sua caratteristica binaria esso è adottato come elemento fondamentale delle operazioni aritmetiche in tutti gli apparecchi elaboratori di impulsi (calcolatori elettronici numerici, contatori elettronici ecc.).

Il m. bistabile a transistori, di tipo integrato, costituisce inoltre l’elemento fondamentale di memoria con cui sono realizzati i circuiti logici sequenziali, per i quali la configurazione del sistema in un certo istante (valutabile tramite i valori logici delle uscite) dipende non soltanto dai valori assunti dalle variabili di ingresso ma anche dalla sua configurazione precedente; caratterizzato da due distinti stati di equilibrio, si presta molto bene alla memorizzazione di un’informazione di tipo binario.

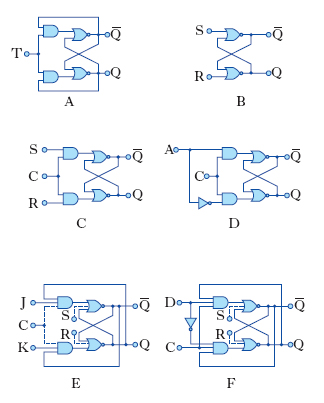

Esistono vari tipi di m. bistabili, per impieghi specifici diversi, che si differenziano tra loro a seconda del numero degli ingressi e per l’azione che i segnali di entrata hanno sulla commutazione. Il m. bistabile T, normalmente impiegato come divisore di frequenza, cambia il suo stato ogni volta che al suo unico ingresso T viene applicato un impulso di comando (trigger); si può avere la commutazione, evidentemente di entrambe le uscite, o durante i fronti in salita o durante i fronti in discesa del trigger (fig. 3A). Il m. bistabile SR, a due ingressi, è realizzato come circuito logico tramite due porte NOR (fig. 3B): uno degli ingressi di ciascuna porta è riservato all’accesso esterno mentre l’altro riceve l’uscita della porta opposta; con la riconduzione dei segnali dall’uscita all’ingresso si realizza una retroazione positiva che stabilizza il circuito in una delle due possibili configurazioni. L’attivazione dell’ingresso S (set), ottenuta con un segnale anche temporaneamente a livello logico 1, forza il m. bistabile nello stato individuato da Q=1 (Ǭ=0), qualunque sia stato il valore precedente di Q; analogamente, l’attivazione dell’ingresso R (reset) determina in ogni caso Q=0 (Ǭ=1), vale a dire l’azzeramento; l’assenza di entrambi i segnali di ingresso non dà evidentemente luogo a commutazione; bisogna viceversa evitare la presenza contemporanea dei segnali di set e di reset, in quanto risulta indeterminata la configurazione finale. Del m. bistabile SR esiste anche la versione sincrona (fig. 3C e D), per la quale le commutazioni precedenti possono avvenire solo in presenza di impulsi di temporizzazione all’ingresso C (clock), che abilita le porte AND poste in entrata. Il m. bistabile JK è realizzato (fig. 3E) con duplice retroazione e non presenta stati di indeterminazione, commutando sempre in corrispondenza della configurazione di entrata J=K=1. Anche di esso esiste la versione sincrona provvista di ingresso c per il clock; molto spesso il m. bistabile JK è anche fornito di ingressi SR asincroni diretti di set e di reset. Nel m. bistabile D si ha un solo ingresso attivo D (fig. 3F); esso presenta in uscita lo stesso livello logico presente in ingresso, in un istante successivo determinato dall’impulso di clock. Come mostrato in fig. 3F può essere realizzato da un m. bistabile JK (o SR) collegando un invertitore tra gli ingressi JK, e trova tipica applicazione nei registri di scorrimento.